# Current Balancing Using a Coupled Inductor Pair in Multi-Parallel Megahertz Wireless Power Transfer Systems

Taiga Osada

Dept. of Electrical, Electronics

and Information Engineering

Nagaoka University of

Technology

Nagaoka, Japan

s245014@stn.nagaokaut.ac.jp

Rintaro Kusui

Dept. of Electrical, Electronics

and Information Engineering

Nagaoka University of

Technology

Nagaoka, Japan

kusui@stn.nagaokaut.ac.jp

Hiroki Watanabe

Dept. of Electrical, Electronics

and Information Engineering

Nagaoka University of

Technology

Nagaoka, Japan

hwatanabe@vos.nagaokaut.ac.jp

Jun-ichi Itoh

Dept. of Electrical, Electronics

and Information Engineering

Nagaoka University of

Technology

Nagaoka, Japan

itoh@vos.nagaokaut.ac.jp

Abstract—This paper proposes a new current balancer for megahertz wireless power transfer (WPT) systems. The small coupled inductors in the proposed method balance the current in the primary side inverters of a WPT system. The coupled inductor is designed based on the area product to achieve the desired current unbalance ratio. The operation of the proposed balancer is tested using a prototype at an operating frequency of 85 kHz. The experimental results demonstrate that the proposed system balances the two inverter currents with an unbalance ratio of 1.22% when the inverters have a 20-degree difference in their output voltages.

Keywords— wireless power transfer, current balancer, seriesseries compensation, circulating current

### I. INTRODUCTION

The parallel operation of inverters enhances the power capacity of compact and lightweight WPT systems operating in high-frequency bands [1]-[3]. However, output voltage unbalance and common-mode voltage differences between inverters generate circuit currents ,which may lead to system failure. At megahertz switching frequencies, nanosecond-level adjustments are required, making precise correction extremely difficult even when using field-programmable gate arrays (FPGAs) [4]. To address this issue, passive current balancers have been proposed to suppress circuit currents without requiring strict control [5].

Both non-isolated and isolated current balancers have been proposed for megahertz WPT systems [6]-[7]. In the non-isolated configurations, only the voltage unbalance between the inverter outputs generates flux, enabling compact balancer designs. Equipping each inverter leg with a transformer prevents short circuits in the balancer. However, the impedance of the balancer becomes low. In contrast, isolated balancers function as isolation transformer, preventing short-circuit currents even when the inverter reference voltages differ. Since the entire output power flows through the transformer, the balancer tends to be large in volume.

This paper proposes a current balancer that uses a compact coupled inductors pair to suppress short-circuit currents caused by common-mode voltage difference and circulating currents resulting from output voltage unbalance. The primary and secondary windings of the coupled inductors are differentially connected to the inverter legs with identical voltage outputs. Magnetic flux is generated only in response to voltage unbalance, significantly reducing the required core volume.

Furthermore, the resonance capacitors present high impedance to DC and low-frequency components of the common-mode voltage due to their series connection with each coupled inductor winding and the transmission coil. Additionally, the coupled inductor pair itself exhibits high impedance to high-frequency common-mode voltage components. As a result, the proposed balancer effectively suppresses short-circuit currents caused by common-mode voltage differences between inverters.

The new contribution of this paper lies in the demonstration of current balancing performance, which is verified through simulations at 6.78 MHz and experimental validation at 85 kHz. The results confirm that the system maintains current balance even when a phase difference exists between inverter output voltages.

### II. PROPOSED SYSTEM

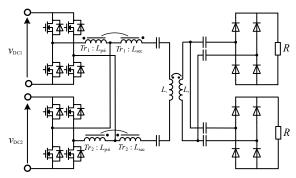

## A. Conventioal system

Fig. 1 shows the configuration of a WPT system using a conventional non-isolated balancer. In this system, the primary windings of the balancer are connected in series with each inverter, while the secondary windings are connected in series with the transmission coil. The balancer is configured to equalize the current through each inverter. The coupled inductors are differentially connected, and the turn ratio  $N_1:N_2$  is set equal to the number of inverters connected in parallel. With this configuration, the average value of the secondary current flows into the primary side, enabling current balancing among the inverters. Because of the differential connection, the magnetic flux in the balancer is generated only in response to

output voltage unbalance, which contributes to the size reduction of the balancer. However, the use of only one coupled inductor per inverter leg lowers the impedance.

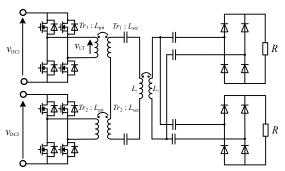

Fig. 2 shows the configuration of a WPT system using a conventional isolated balancer. In this case, the primary side of the balancer is connected in parallel with the output of each inverter, and the secondary side is connected in series with the transmission coil. This configuration allows the balancer to function as an isolation transformer, electrically isolating the inverters. Isolated balancers have the advantage that current balancing is possible depending on the transformer turn ratio. However, since the transformer must transfer the entire output power of the inverters, the volume of the balancer increases significantly.

# B. Proposed system

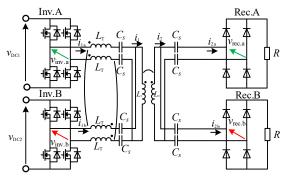

Fig. 3 shows the circuit configuration of the proposed WPT system incorporating a current balancer with a pair of coupled inductors. In this configuration, a series-series compensation topology is employed, where the resonant capacitor and the transmission coil are connected in series. This configuration allows the average output voltages of the inverters are equalized at the output side of the balancer. The resonant capacitor is split into two parts, each connected in series with one of the coupled inductors. The coupled inductors are differentially connected to the output lines of the inverter legs that produce the same voltage. In the proposed system, the divided capacitors present high impedance to the DC and low-frequency components of the common-mode voltage of each inverter. Therefore, even when the inverters are connected in series with the power supply, large circulating currents do not occur. In addition, the impedance of the coupled inductors helps to attenuate high-frequency components. As a result, the proposed current balancer achieves a compact design while maintaining high impedance against common-mode currents.

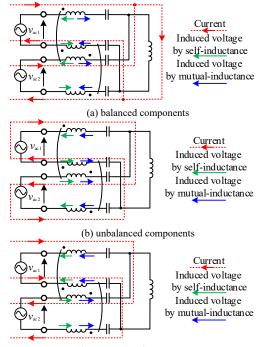

# C. Proposed balancer configlation

An inverter output-voltage imbalance makes the flux in the series-aiding connected inductors add rather than cancel, preventing mutual cancellation. This results in a net magnetic flux in the core, which induces a voltage. The induced voltage offsets the average voltage difference between the inverters. As a result, the average output voltages of the inverters are equalized at the output side of the balancer. The common-mode component is the ground-referenced common-mode voltage generated by currents flowing from each inverter leg. In the case of Inv.A, the current flowing between both output lines is significantly attenuated by the high impedance of the split resonant capacitors and coupled inductor, which effectively suppresses the low-frequency component of the common-mode current. These voltage components allow the system to operate as a balancer with respect to the resulting current behavior. Thus, the proposed current balancer achieves both compactness and high impedance against common-mode currents.

Fig. 1. Non-isolated conventional system.

Fig. 2. Isolated conventional system.

Fig. 3. Multi-parallel WPT system for coupled inductors.

# III. DESIGN OF COUPLED INDUCTOR

# A. Design policy of coupled inductor

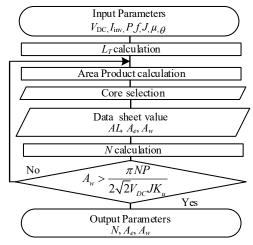

Fig. 5 shows a flowchart illustrating the design procedure for the coupled inductor. In this study, a ferrite core is used for the coupling inductor. Due to its high permeability, the leakage flux can be ignored. Therefore, the coupling coefficient is 1. Reference [8] describes the design of the transmission coil and resonant capacitor, which is omitted here. This also applies to two parallel connections. The required self-inductance  $L_T$  is determined in order to suppress circulating currents. The self-inductance  $L_T$ . The combination of  $L_T$  and the peak magnetizing current,  $I_m$  yields the calculated area product  $A_{P,cal}$ . The design selects a magnetic core whose area product exceeds  $A_{P,cal}$ . A toroidal core is assumed, and the transmission frequency f and  $L_T$  dictate the choice of core material. The core datasheet

provides the AL value, core cross-sectional area  $A_e$ , and window area  $A_W$ . The required number of turns N is calculated to achieve the desired  $L_T$ . The window area is estimated from the inverter output currents  $I_{1a}$ ,  $I_{1b}$ , and the allowable current density J. If the computed window area exceeds  $A_W$ , the procedure selects an alternative core. The estimation of the required window area uses the inverter output currents  $I_{1a}$  and  $I_{1b}$ , along with the allowable current density J. If the estimated window area exceeds  $A_W$ , the design process selects an alternative core.

## B. Design of coupled inductor

The inverter currents  $I_{1a}$  and  $I_{1b}$  consist of balanced components with the same sign and unbalanced components with opposite signs.  $I_{1a}$  and  $I_{1b}$  are expressed as

$$I_{1a} = \frac{R}{4\omega^2 M^2} \frac{V_{inv.a} + V_{inv.b}}{2} + \frac{1}{2j\omega(2L_T - L_1)} \frac{V_{inv.a} - V_{inv.b}}{2}$$

(1),

$$I_{1b} = \frac{R}{4\omega^2 M^2} \frac{V_{inv.a} + V_{inv.b}}{2} - \frac{1}{2j\omega(2L_T - L_1)} \frac{V_{inv.a} - V_{inv.b}}{2}$$

(2).

The self-inductance  $L_T$  is calculated from the maximum allowable phase difference of each inverter output voltage and any unbalance ratio. The unbalanced ratio is defined as the amplitude ratio of the balanced and unbalanced components of the inverter current, as expressed in (1) and (2). When the inverter output voltages have no phase difference, and the ratio of the inverter current under this condition to the unbalanced component when there is a phase difference  $\theta$  between the output voltages of the inverters is defined as the inverter unbalance ratio  $\varepsilon_{l,inv}$ , The  $\varepsilon_{l,inv}$  is expressed as

$$\varepsilon_{I_{\perp inv}} = \frac{2\omega M^2 \sqrt{2 - 2\cos\theta}}{R(2L_T - L_1)}$$

(3).

The  $L_T$  is expressed as

$$L_T = \frac{\omega M^2 \sqrt{2 - 2\cos\theta}}{R\varepsilon_{i\_inv}} + \frac{L_1}{2}$$

(4).

The area product  $A_{p\ cal}$  is expressed as

$$A_{p\_cal} = \frac{L_T \cdot i_m^2}{J \cdot B_m \cdot K_u} \tag{5},$$

where the coil space factor is  $K_{\rm u}$ , the maximum winding current density is J, and the maximum flux density of the core is  $B_m$ . The area product value larger than the value obtained from  $A_{p\_cal}$  is selected for the core.

The number of turns N is calculated from  $L_T$  and AL values. The N is expressed as

$$N = \sqrt{\frac{L_T}{AL}} \tag{6}.$$

The  $A_W$  is a value selected from the datasheet. The  $A_W$  is compared to the minimum core winding area derived from N in (6). The comparison is expressed as

$$A_{w} > \frac{\pi NP}{2\sqrt{2}V_{DC}JK_{u}} \tag{7},$$

And a core satisfies (7) is selecteded.

(c) common mode components

Fig. 4. Operation of proposed system.

Fig. 5. Design procedure flowchart.

### IV. SIMULATION RESULT

### A. Parameter determination

Table 1 lists the simulation parameters. The input voltage is set to 200 V, the rated power to 2 kW, and the transmission frequency to 6.78 MHz. The coupling coefficient of the coupled inductors are assumed to be 1, and the coupling coefficient of the transmission coil was set to 0.2.

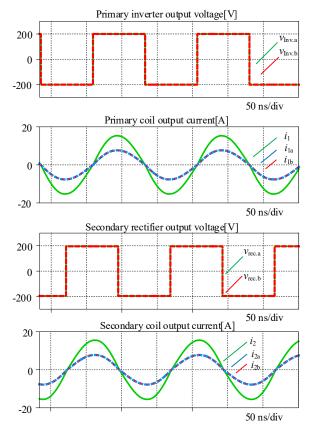

### B. Operating waveform without phase difference

Fig. 6 shows the operating waveforms when the output voltages of the inverters are equal. Each inverter delivers 2 kW, of output currents of Inv.A and Inv.B are 5.37 Arms. The current

Fig. 6. Simulated waveforms of the proposed system without phase difference between primary inverters.

and voltage waveforms on both the primary and secondary sides are in phase. In contrast, the phase difference between the primary and secondary currents of the transmission coil is 90 degrees. These results confirm that the proposed balancer does not affect the resonance condition.

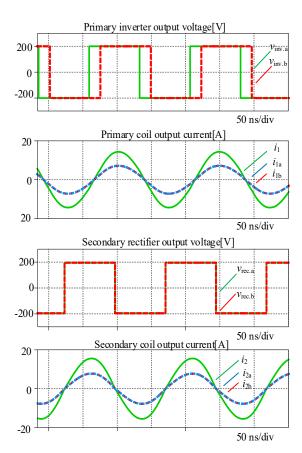

## C. Operating waveform with phase difference

Fig. 7 shows the proposed system operation with the voltage phase difference of Inv.B changed to 16 ns (20 degrees). This delay accounts for variations in the gate drive unit (GDU) and switching devices. Under these conditions, each inverter delivers 1.76 kW of output power, and the output currents of Inv.A and Inv.B both reach 5.10 A. The output power of the inverters is 1.76 kW, and the output currents of Inv. A and Inv. B is 5.10 A. Although the phase difference causes unbalance in each inverter, the output currents of the inverters match. The coupling inductor generates an induced voltage in response to the circulating current appears, and this induced voltage cancels the difference in inverter output voltages. This cancellation maintains the resonant condition and suppresses circulating current. The phase difference in the inverter voltage causes the balancer to compensate for the output voltage unbalance. Therefore, the power factor is reduced, and the transmitted power is decreased. This imbalance leads to current nonuniformity and circulating currents between inverters. This

Fig. 7. Simulated waveforms of the proposed system for a phase difference of 1.3μs (20 degrees) between primary inverters.

| TABLE I.                 | SIMULATION CONDITION |          |  |

|--------------------------|----------------------|----------|--|

| Prameters                | Symbol               | Value    |  |

| DC voltage               | $V_{DC}, V_{DC2}$    | 200 V    |  |

| Rated output power       | $P_{out}$            | 2 kW     |  |

| Transmission frequency   | f                    | 6.78 MHz |  |

| Coupling coefficient     | k                    | 0.2 -    |  |

| Transmission coil        | $L_1, L_2$           | 1.90 μΗ  |  |

| Filter inductor          | $L_{TI}$ , $L_{T2}$  | 7.56 µH  |  |

| Series capacitors for SS | $Cs_1, Cs_2$         | 289 pF   |  |

causes the inverter to cause a short circuit during each inverter switching.

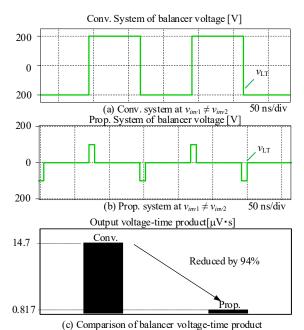

# D. Comparison with insulated balancers

Fig. 8 shows a comparison of the balancer voltages of the conventional and proposed system. Fig. 8(a) shows the output voltage of the isolated balancer. The conventional system applies the full inverter output voltage to the transformer, which increases the magnetic flux and consequently enlarges the balancer volume. In contrast, Fig. 8(b) shows that the proposed system applies only the voltage difference between the inverter outputs to the balancer. This differential application limits the magnetic flux in the coupled inductor, which depends on the product of voltage and time. The design directly links the balancer volume to this magnetic flux, allowing the voltage-time

product to serve as an indicator of balancer size. Fig. 8(c) shows a comparison of voltage-time products between the proposed and conventional systems. The proposed system reduces the voltage-time product by 94.4%. If the design maintains the same magnetic flux density, the reduction in flux enables a proportional decrease in the core cross-sectional area. Assuming the same magnetic flux density and path length, the proposed system also reduces the balancer volume by 94.4%.

### V. EXPERIMENTAL VERRIFICATION

### A. Experimental conditions

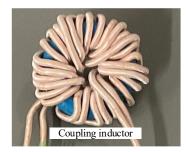

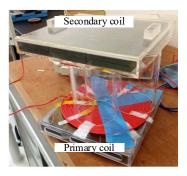

This study evaluates the proposed current balancer under practical conditions by using a lower, more manageable frequency of 85 kHz. The test bench connects the power supplies in parallel to verify the balancing operation. The DC voltage is maintained at 200V, and the rated power is 2 kW. Fig. 9 shows the fabricated coupled inductor. A toroidal ferrite core is used, wound with 1.25mm litz wire at a 1:1 turn ratio,resulting in a mutual inductance of 600  $\mu H.$  Fig. 10 shows the fabricated transmission coil. The coil consists of spiral-wound conductors arranged on matching cores, with the primary and secondary windings facing each other across a 150 mm gap. This configuration achieves a coupling coefficient of 0.2.

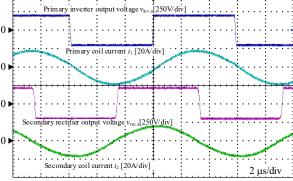

# B. Operating waveform without phase difference

Fig. 11 shows the operating waveforms without phase difference between primary inverters. The waveforms include the output voltages of Inv.A and Rec.A, along with the transmission coil current. The measurements record output currents of 5.83 A for both Inv.A and Inv.B. The approximately 90 degree phase shift between primary and secondary transmission coil currents confirms resonant power transfer.

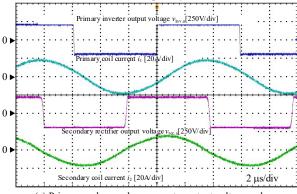

# C. Operating waveform with phase difference

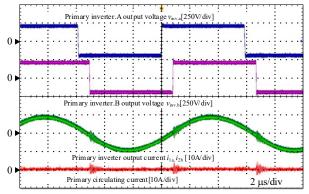

Fig. 12(a) shows the operating waveforms under a phase difference of 1.3 µs (20 degrees). This delay was set to match the phase difference used in the 6.78 MHz simulation. From the waveforms, it is observed that the power factors of both the primary and secondary sides of the series-series compensated network are approximately 1. As a result, the output currents of Inv.A and Inv.B are 5.69 A and 5.68 A, respectively. The difference between the two output currents is 0.18%, indicating that the proposed balancer achieves current balancing with a deviation of only 0.18% from the average current. Fig. 12(b) shows the waveforms of Inv.A and Inv.B output voltages, the primary-side current of the transmission coil, and the circulating currents between the inverter outputs under the same 1.3 µs phase difference. In this case, the output currents of Inv.A and Inv.B are 6.65 Arms and 6.57 Arms, respectively, with a difference of 1.22%. This confirms that the proposed balancer achieves the current balance with a deviation of only 1.22% from the average current. The coupled inductor was designed for a target imbalance ratio of 1%, and the experimental results validate that the proposed design method meets this target. Table 2 summarizes the measured voltages, currents, and power values on both the primary and secondary sides of the proposed circuit. It also compares the transmitted

Fig. 8. Balancer voltage of conventional and proposed system.

Fig. 9. Prototype coupling inductor.

Fig. 10. Prototype transmisson coil.

power under different phase conditions. When no phase difference is present, the transmitted power is 2.40 kW with an efficiency of 94.2%. When a 1.3 µs phase difference is introduced, the transmitted power is 2.36 kW, and the efficiency decreases to 91.8%. This efficiency reduction is attributed to the balancer compensating for voltage unbalance under phase-shifted conditions, which results in additional power loss.

### VI. CONCRUSION

This paper proposes a current balancer that uses a pair of coupled inductors for parallel operation in high-capacity wireless power transfer systems. The addition of a pair of coupled inductors to the series–series compensation topology, in which the resonant capacitor and transmission coil are connected in series, realizes the proposed system. Simulation results confirm that the inverter currents remain balanced at high frequencies. Future work will focus on developing a compensation method for leakage inductance in the coupled inductors during megahertz operation.

### REFERENCES

- Y. Neba, T. Ohno, S. Kusuki "PWM Dual Current Source Inverter Connected in Parallel for Induction Motor Drives", IEEJ Journal of Industry Applications, Vol. 13, No.4 pp. 417-425, 2024

- [2] Y. Funaki, K. Wada " Gate Drive Circuit Implementation for Parallel Connection of Power Devices Considering Parasitic Inductance", IEEJ Journal of Industry Applications, vol. 12, no. 2, pp. 176-182, 2023

- [3] T. Sawada, H. Tadano, K. Shiozaki, T. Isobe, "Continuous Operation of a Half-Bridge with Multi-Parallel GaN Power Devices for Increased Current Capability," IEEJ Journal of Industry Applications, vol. 12, No.4, pp. 695-700, 2023

- [4] L. Giorgio, I. Takehiro, F. Hiroshi and H. Yoichi "Secondary-side-only Phase-shifting Voltage Stabilization Control with a Single Converter for WPT System with Contant Power Load", IEEE Journal of Industry Applications, vol. 8, no. 1, pp. 66-74, 2018

- [5] N. K. Trung and K. Akatsu, "Design challenges for 13.56MHz 10 kW resonant inverter for wireless power transfer systems", 2019 10th International Conference on Power Electronics and ECCE Asia, 2019

- [6] S. Suzuki. O. Satoshi, K. Orikawa, "Miniaturization and Current Detection of Coupled-Inductor Circuit for Reducing Cross Currents of Modular Paralleled Power Converters", IEEJ Transactions on Industry Applications, vol. 143, no. 3, pp. 177-186, 2023

- [7] M. Yamaguchi, K. Kusaka, J. Itoh: "Megahertz High-power WPT system with Parallel-connected inverters using current balance circuit" ECCEurope, vol. 1, no. 0925, pp. 2022

- [8] R. Bosshard et al., IEEE Journal of Emerging and Selected Topics in Power Electronics, Vol.3, No.1, pp.50–64 2015

TABLE II. CIRCUIT PARAMETERS Prameters Symbol Value  $V_{DC}, V_{DC2}$ DC voltage 200 Rated output power  $P_{out}$ kW Transmission frequency 85 kHz Coupling coefficient 0.2 μН Transmission coil  $L_1,L_2$ 151 Design coupled inductors 603 μН Measesurement coupled inductors  $L_T$ μΗ 23.1 Series capacitors for SS Cs. Cs. nF AL2540 nH/m AL value N<sub>AL</sub> value 15  $N_{AI}$ turn N<sub>max</sub> value 40 turn  $A_{p\_cal}$  value  $A_{p\_care}$  value 754 4891 mm mm  $\dot{Vol}_L$  value mm Primary inverter output voltage vin

Fig. 11. Experimental waveform of proposed system without phase difference between primary inverters.

(a) Primary and secondary converter output voltage and coil currents waveform.

(b) Primary inverter output voltages and currents

Fig. 12. Experimental waveform of proposed system with 1.3 μs (20 deg.) phase difference between primary inverters.